PC Technology Trends 2022 - CPU Edition

At the beginning of 2022, we will deliver "PC Technology Trends" that predicts trends in personal computer hardware technology. This article is for the CPU. With Alder Lake, which was launched at the end of 2021, Intel has finally achieved performance that exceeds AMD's Ryzen 5000 series. And 2022 is likely to be an even more intense year, with AMD counterattacking and Intel aiming to catch up.

| ◆Links to Related Articles (Published January 1, 2022) PC Technology Trend 2022 - Process Edition (this article) PC Technology Trend 2022 - CPU Edition (January 2022) PC Technology Trend 2022 - GPU (Published January 4, 2022) PC Technology Trend 2022 - Memory/DRAM (Published January 5, 2022) PC Technology Trend 2022 - Flash Storage (Published January 5, 2022) Posted January 6) PC Technology Trends 2022 - Chipset Edition |

|---|

***

Continuing from the process edition, next is the CPU edition. By the way, it was announced on November 4, 2021 that VIA Technologies, which has practically not introduced any new products, has sold its subsidiary Centaur Technology to Intel for $125 million. rice field. This is an announcement from TWSE (Taiwan Stock Exchange), and neither VIA Technologies nor Intel has released any information regarding this matter.

With this acquisition, Intel is transferring Centaur Technologies employees (some of Centaur's employees) to Intel. On the other hand, VIA Technologies still holds the rights to the IP that Centaur has developed so far. Therefore, VIA Technologies can continue to sell VIA Nano, etc., but the reality is that they can no longer develop new cores, and VIA Technologies itself has shifted to an Arm-based solution business. It won't come out.

As a result, as vendors other than Intel and AMD, Zhaoxin in China, which received an IP license from Centaur via VIA Technologies, Hygon in China, which received an IP license from AMD, and SiS, which acquired the former RiSE Technology, The entire SiS550 series (RiSE mP6-based SoC) assets have been acquired, and only Taiwanese DM&P, which is expanding and providing them in-house, has become. That's why the CPU edition is only Intel and AMD.

Intel CPU(Photo01)

Alder Lake successfully released in November 2021. As we have already delivered the performance review, the performance is sufficiently far beyond the Ryzen 5000 series.

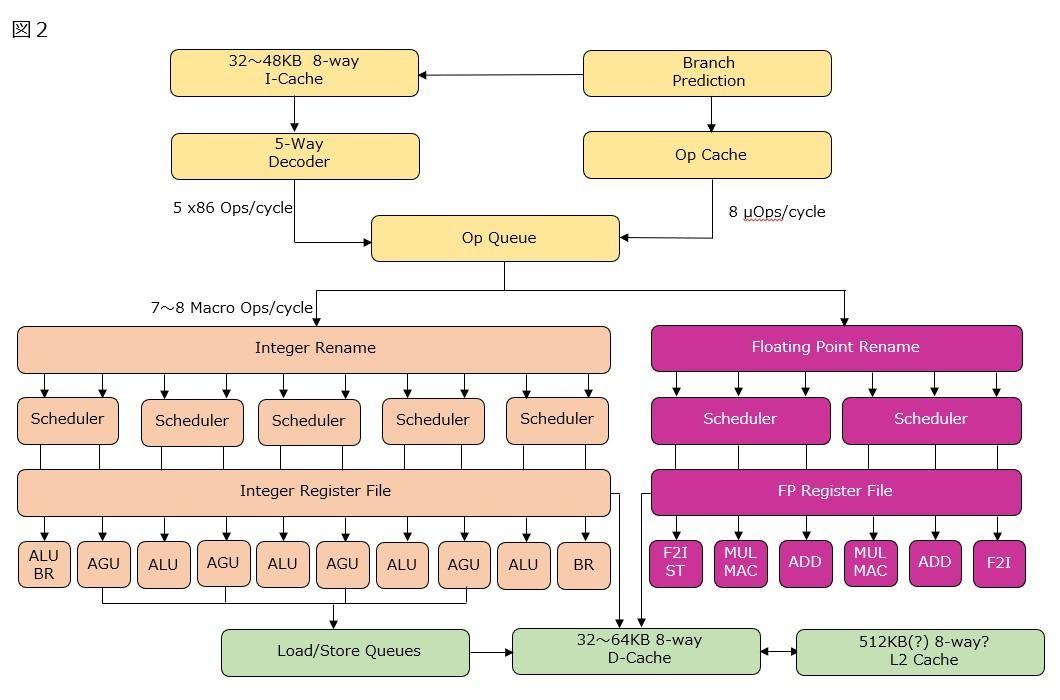

However, it's true that I can't deny the feeling that I made it in a hurry. Looking at the analysis by RMMA, Front End has a decoder of 6 instructions / cycle at peak and 5 instructions / cycle (both are converted to x86 instructions) even if it is effective. I wouldn't be surprised if the IPC goes up by about 25%. However, the actual performance, for example, when looking at the Dhrystone 1T results, which is easy to understand, is certainly high, but the growth is still in the 10% range, so it seems that there is still an internal bottleneck. Some of the RMMA results and Sandra's results also show this trend. Is Sandra's Inter-Thread Latency the obvious one? Somehow slow overall. Local L2 access is slow, and via L3 is even slower. One of the reasons is the adoption of Hybrid Architecture, and I think that Latency on the E-Core side is holding back, but my honest impression is that there is still a lot of room for improvement.

Also, as I mentioned earlier in Intel's Process section, Intel 7 is certainly much better than 14nm++, but the transistor density has not increased as much as I thought, and the upper limit of operating frequency itself is not much different from 14nm++. It feels like Alder Lake is the best configuration within that frame. In that sense, it can be said that there is no room for Intel 7 to increase the number of cores or improve the operating frequency with the next Raptor Lake. Somehow, it feels like Alder Lake was designed to maximize performance within the framework of Intel 7.

That Alder Lake will likely see additional SKUs announced at the upcoming CES. In the first place, as shown here, the only ones announced in November 2021 were Core i5/7/9 K/KF without magnification lock. Of course, there should be a normal version SKU without K, and a T SKU for power saving with reduced TDP, and it may be necessary to add Core i3 and Pentium/Celeron.

Now, regarding this Core i3 and below, there is talk of producing this with TSMC's N5. The reason is simple: the production capacity of Intel 7 seems not so high. As I wrote in this article, the number of K SKUs shipped in the fourth quarter of 2021 is only a few hundred thousand. Intel still does not disclose Alder Lake's die size (but Wafer is fine), so I don't know the exact size, but Rocket Lake is close to 220 square mm. Assuming that Alder Lake is 200 square mm, the number of dies that can be taken from one 300mm wafer is about 300. Even if the Yield is high enough, this is only a few thousand wafers (perhaps about 1,000?). Well, if the Yield is a little low, maybe around 2,000? It is unknown how long they have been making and storing until shipment in November 2021, but it is likely that even at present, the monthly production order is several thousand (and it does not reach 3,000). If we can produce 2,000 pieces per month, we can produce 6,000 pieces in three months. That's 1.8 million at 300 per wafer, which is pretty close to "shipping more than 2 million by the end of the first quarter of 2022", but in reality there are some defective ones, so it's a little more. 3,000 pieces per month, 9,000 pieces / 2.7 million chips manufactured in 3 months, shipping 2 million pieces + α is a realistic number.

So, 2 million in 3 months is definitely not a good enough number. Since the figures for the full year of 2021 have not yet been released, in terms of figures for the third quarter of 2021, CCG (Client Computing Group) sales are $9664M. The absolute amount of ASP is of course undisclosed, but for example, Core i7-12700K ASP is $399-$409, so if it is $400, even if the total amount is Core i7-12700K, it will not reach this sales unless it sells about 24 million units. . Of course, considering that the actual ASP is not that expensive (it won't go to the $200 level), it is necessary to mass-produce chips with a figure close to that, if not 50 million, and the production volume of Intel 7 is an order of magnitude short. However, the 10nm SuperFin used in TigerLake and IceLake-SP does not have enough operating frequency, and there is no plan to return to 14nm now. As a result, I think that the production of Alder Lake's Low End (Celeron to Core i3) grade was outsourced to TSMC.

Originally, Intel 7 has specifications that are almost similar to TSMC N7P, and by switching to N5, the area size can be reduced by 45%, power consumption can be reduced by 20%, or operating frequency can be improved by 15%. be done. Originally, Alder Lake for Desktop has a 6C + 0E configuration in addition to the 8P + 8E configuration (Photo02) is published here, and it seems that this 6C + 0E + 32EU product is entrusted to TSMC. In short, Core i3 or less. If two P-Cores and all E-Cores are removed, the die size will fit in about 160 square mm even if Intel 7 is used. After cutting, it becomes around 90 square mm. Then, it is calculated that more than 700 pieces can be obtained from one 300mm wafer, and it is expected that the chip cost will be reduced enough to pay even if it is outsourced. In addition, because the number of pieces that can be obtained is large, for example, a monthly production of 10,000 pieces can secure 7 million pieces, and 21 million pieces can be secured in 3 months. It seems that orders for 14nm generation products will be canceled soon, but the cancellation of orders does not mean that shipments will be stopped immediately, and shipments of 14nm generation products will continue for a while. It won't be difficult to maintain shipments close to 50 million units (the problem is whether TSMC's N5 can secure 10,000 units per month?). This launch could start as early as the first quarter.

Now, next is Raptor Lake. In fact, the codename for Raptor Lake has been revealed since last year. First clearly shown is the Product List page of SATA-IO (Photo03). There are two PCHs at the end of this, but both are "Codename Alder-Raptor Lake PCH-S SATA Controller", suggesting that the PCH is the same for Alder Lake and Raptor Lake. After that, information came out from here and there, and the existence of Raptor Lake is already quite certain.

The Raptor Lake, as I mentioned earlier, is expected to be manufactured at TSMC's N3. there are two reasons

It's around. However, can Alder Lake be completely replaced by Rapter Lake? I think this is also difficult. The reason is the capacity of TSMC N3. I introduced Mr. Tsuyoshi Hattori's article on Process earlier, but before the harassment of AMD, Intel lacked the manufacturing capacity for advanced processes to the extent that they wanted all the capacity of Fab18B if they needed it. This will be fulfilled after 2024 when Intel's Fab, which is currently under construction in Arizona, will start operation. We'll have to rely on TSMC for at least 2022-2023.

However, I personally had doubts about N3. This is because, as explained earlier in the TSMC process, mass production of the N3 itself is expected to start in the second quarter of 2022, but mass production other than Apple is expected to be delayed to 2023. Rather, N4 or N4P seemed more likely. However, with such reports, it may be possible to secure it unexpectedly.

So the process seems to go with N3, but the information I've heard so far about other configurations is

or something like that. The core itself seems to be basically the same as Alder Lake's Golden Cove + Gracemont, although there is some work to be done. Could it be some improvement? Rather, as a design team, it will be a lot of work to make the core that has been designed for Intel compatible with TSMC's N3.

Although it is not confirmed information elsewhere, power consumption may be reduced somewhat by making it a process of TSMC. In addition, there is also talk of mounting a DLVR (Digital Linear Voltage Regulator) on the package side. This is a story described in a patent acquired by Intel in July 2021, and it is intended to improve the efficiency of power supply by installing a FIVR (Fully Integrated Voltage Regulator) or DLVR in the CPU package. , In the example described in the patent, when a current of 40A flows through the core, it is possible to improve power consumption efficiency by up to 25% (Photo04). Will this be installed in Raptor Lake? That's what I'm talking about.

However, what this patent means is that when the load is medium, there is a mismatch between the voltage that the core originally needs to drive and the voltage that is actually supplied, and this is corrected by the on-chip voltage regulator. It is a story to prevent a useless voltage increase by covering. The reason why there is a mismatch is that the PMIC (Power Management IC) is outside the package, and it takes time to issue a request from the CPU core and change the voltage according to the load. Therefore, the CPU side always requests a slightly higher voltage than the required voltage, and even if it is necessary to suddenly increase the voltage, the request is issued to the PMIC and a margin is earned until it is reflected. , By placing a second voltage regulator on the package, it is possible to quickly supply a voltage close to the required voltage, eliminating the need to wastefully request a higher voltage. As a result, loss is reduced, and power consumption can be reduced by up to 25%. However, this is effective in the case of a medium load where voltage fluctuations occur, but when it is fully driven, there is no voltage change or hesitation, and the voltage is always set to the maximum setting, so for example Photo04 In the case of 70A, it can be seen that the improvement rate is 0. In that sense, it's useful for Mobile, and it may be appreciated by T SKUs on Desktop, but it doesn't contribute to lowering the TDP (or rather, PL1 or PL2) of K SKUs that are fully powered.

Originally, Intel integrated FIVR into the CPU package in the Haswell generation and removed it in the Skylake generation. This is because the on-chip FIVR can handle high power efficiently, but is less efficient at low power (mainly due to inductance package limitations). AMD takes this into account and implements an LDO regulator, and it's a little interesting that the two companies' responses are spectacularly different.

Returning to the story, it is a bit of a mystery whether this DLVR is really installed in Raptor Lake. I wouldn't be surprised if it was implemented, but will it be done with Raptor Lake, which uses TSMC's process? It's quite a mystery, and I feel like I'm going to do it at the next Meteor Lake.

The last is Meteor Lake, but there is no concrete story yet. However, for example, although the decoder was called Peak 6 instructions / cycle, Sustained had 5 instructions / cycle, but I expect improvements such as the number of Decode instructions in Sustained to increase a little more and the Latency of Cache to decrease. It looks like it would be fine. Also, in this generation, it will be a complete module configuration, and CPU Die, I / O Die, and GPU Die will be packaged with Foveros.

In the slide at the time of the announcement of this package, Intel 4, it was drawn like three dies, CPU, PCH, and GPU, but in reality it is CPU Tile, SoC Tile, and GT Tile as shown in Figure 1 In addition, there seems to be an IOE Tile that contains PCIe and Thunderbolt controllers.

However, Figure 1 is for Mobile, and if it is for Desktop, IOE Tile may be omitted. As a writer, I thought that the CPU Tile would be separate, for example, the P-Core Tile and the E-Core Tile, but it seems that it will not be divided to that extent.

Also, regarding SoC Tile, there are rumors that GNA will be abolished in this Meteor Lake generation and instead the AI core of Movidius acquired by Intel will be included. Although Intel GNA boasts a high performance/power consumption ratio, the absolute processing performance is rather low, so we often hear that the performance is insufficient even if you try to use it via Intel's OpenVINO. Well, there is also a story that applications that use OpenVINO are not suitable for GNA. I may have decided to switch.

Now this Meteor Lake itself is packaged with Foveros. Looking at the video in the release "Intel Breakthroughs Propel Moore's Law Beyond 2025" announced by Intel on December 11, 2021, the example of using Foveros (Photo05) is Meteor Lake, and there are many more. It is said that it is possible to combine Tiles of different sizes (Photo06) and Tiles of various sizes (Photo07). Meteor Lake is a conservative configuration that takes a safety measure because it is the first generation of processors with a Tile configuration for consumers, and further subdivision of Tile may be after Meteor Lake.

As mentioned in Process, this Meteor Lake is Intel 4. However, in the case of such Multi-Tile, "Which one is manufactured by Intel 4?" For example, CPU Tile and GPU Tile may be Intel 4, and SoC Tile and IOE Tile may be Intel 7. We'll have to wait a little longer to find out more about this.