PC Technology Trends 2022 – CPU Edition

Začátkem roku 2022 dodáme „Trendy technologie PC“, které předpovídají trendy v technologii hardwaru osobních počítačů. Tento článek je pro CPU. S Alder Lake, který byl spuštěn na konci roku 2021, Intel konečně dosáhl výkonu, který překonává AMD Ryzen řady 5000. A rok 2022 bude pravděpodobně ještě intenzivnější rok s protiútokem AMD a Intel se hodlá dohnat.

| ◆Odkazy na související články (Zveřejněno 1. ledna 2022) PC Technology Trend 2022 – Process Edition (tento článek) PC Technology Trend 2022 – CPU Edition (leden 2022) PC Technology Trend 2022 – GPU (Publikováno 4. ledna 2022) PC Technology Trend 2022 – Paměť/DRAM (Publikováno 5. ledna 2022) PC Technology Trend 2022 – Flash Storage (Publikováno 5. ledna 2022) Zveřejněno 6. ledna PC Technology Trends 2022 - Edice čipové sady |

|---|

***

Pokračujeme v edici procesu, další je edice CPU. Mimochodem, 4. listopadu 2021 bylo oznámeno, že společnost VIA Technologies, která prakticky nepředstavila žádné nové produkty, prodala svou dceřinou společnost Centaur Technology společnosti Intel za 125 milionů dolarů.rýžové pole. Toto je oznámení od TWSE (Taiwan Stock Exchange) a ani VIA Technologies ani Intel nezveřejnily žádné informace týkající se této záležitosti.

Touto akvizicí Intel převádí zaměstnance Centaur Technologies (některé ze zaměstnanců Centaur) na Intel. Na druhou stranu VIA Technologies stále drží práva na IP, které Centaur doposud vyvinul. VIA Technologies proto může nadále prodávat VIA Nano atd., ale realita je taková, že již nemohou vyvíjet nová jádra a samotná VIA Technologies se přesunula na řešení na bázi Arm.

V důsledku toho, jako dodavatelé jiní než Intel a AMD, Zhaoxin v Číně, který získal IP licenci od Centaur prostřednictvím VIA Technologies, Hygon v Číně, který obdržel IP licenci od AMD, a SiS, který získal dřívější RiSE Technologie, Byla získána celá aktiva řady SiS550 (SoC založená na RiSE mP6) a stal se jím pouze tchajwanský DM&P, který expanduje a poskytuje je interně. Proto je CPU edice pouze Intel a AMD.

Intel CPU (Photo01)

Alder Lake úspěšně vydán v listopadu 2021. Jak jsme již uvedli výkonnostní recenzi, výkon je dostatečně daleko za Ryzeny řady 5000.

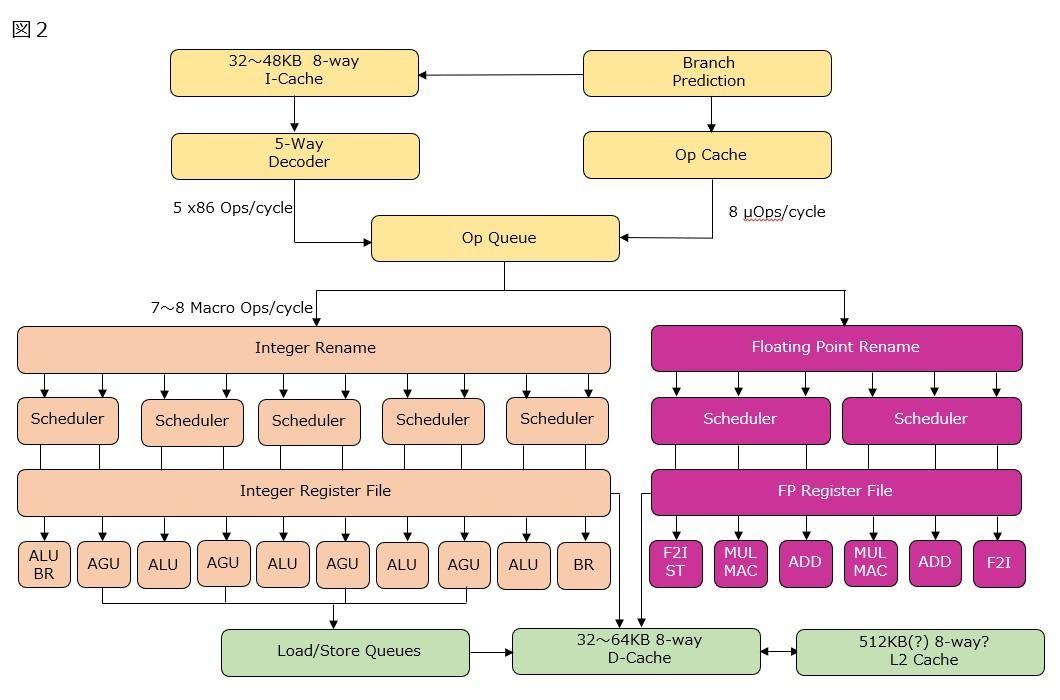

Je však pravda, že nemohu popřít pocit, že jsem to udělal narychlo. Když se podíváme na analýzu RMMA, Front End má dekodér 6 instrukcí / cyklus ve špičce a 5 instrukcí / cyklus (obě jsou převedeny na instrukce x86), i když je to efektivní. Nedivil bych se, kdyby IPC vzrostl o asi 25 %. Nicméně pokud jde o skutečný výkon, pokud se podíváte na výsledky Dhrystone 1T, které jsou snadno pochopitelné, je jistě vysoký, ale stále roste pouze v rozmezí 10 %, takže se zdá, že stále existuje vnitřní úzké hrdlo. Některé výsledky RMMA a výsledky Sandry také ukazují tento trend. Je Sandřina mezivláknová latence zjevná? Celkově nějak pomalu. Místní L2 přístup je pomalý a přes L3 je ještě pomalejší. Jedním z důvodů je přijetí Hybrid Architecture a myslím si, že Latency na straně E-Core se drží zpátky, ale můj upřímný dojem je, že je stále velký prostor pro zlepšení.

Také, jak jsem již zmínil dříve v části Process Intel, Intel 7 je určitě mnohem lepší než 14nm++, ale hustota tranzistorů se nezvýšila tak, jak jsem si myslel, a horní hranice samotné pracovní frekvence se příliš neliší od 14nm++ Zdá se, že Alder Lake je nejlepší konfigurace v tomto rámci. V tomto smyslu se dá říci, že pro Intel 7 není prostor pro navýšení počtu jader nebo vylepšení pracovní frekvence s dalším Raptor Lake. Nějak to vypadá, že Alder Lake byl navržen tak, aby maximalizoval výkon v rámci Intel 7.

To Alder Lake, na nadcházejícím CES, budou pravděpodobně oznámeny další SKU. Za prvé, to, co bylo oznámeno v listopadu 2021, bylo pouze Core i5/7/9, K/KF bez zámku zvětšení, jak je znázorněno zde. Samozřejmostí by měla být běžná verze SKU bez K nebo T SKU pro úsporu energie se sníženým TDP a možná bude nutné přidat Core i3 a Pentium/Celeron.

Nyní, pokud jde o tento Core i3 a nižší, hovoří se o jeho výrobě pomocí N5 od TSMC. Důvod je jednoduchý: výrobní kapacita Intel 7 se nezdá být tak vysoká. Jak jsem psal v tomto článku, počet K SKU odeslaných ve čtvrtém čtvrtletí roku 2021 je pouze několik set tisíc. Intel stále nezveřejňuje velikost matrice Alder Lake (ale Wafer je v pořádku), takže přesnou velikost nevím, ale Rocket Lake se blíží 220 mm čtverečních. Za předpokladu, že Alder Lake má 200 čtverečních mm, bude počet matric, které lze odebrat z jednoho 300mm plátku, kolem 300. I když je výtěžek dostatečně vysoký, jedná se o několik tisíc plátků (možná asi 1000?). No, pokud je výnos trochu nízký, možná kolem 2 000? Není známo, jak dlouho se vyráběly a skladovaly do expedice v listopadu 2021, ale je pravděpodobné, že i v současnosti je měsíční výrobní zakázka několik tisíc (a nedosahuje 3000). Pokud dokážeme vyrobit 2000 kusů za měsíc, můžeme vyrobit 6000 kusů za tři měsíce. To je 1,8 milionu při 300 na wafer, což je docela blízko k „odeslání více než 2 milionů do konce prvního čtvrtletí roku 2022“, ale ve skutečnosti jsou některé vadné, takže budeme mít o něco více. 3 000 kusů za měsíc, 9 000 kusů / 2,7 mil. vyrobených čipů za 3 měsíce, expedice 2 mil. kusů + α je reálné číslo.

Takže 2 miliony za 3 měsíce rozhodně nejsou dost dobré číslo. Vzhledem k tomu, že údaje za celý rok 2021 ještě nebyly zveřejněny, z hlediska údajů za třetí čtvrtletí roku 2021 jsou tržby CCG (Client Computing Group) 9664 milionů USD. Absolutní částka ASP samozřejmě není zveřejněna, ale například Core i7-12700K ASP je 399-409 $, takže pokud je to 400 $, i když celková částka je Core i7-12700K, nedosáhne těchto prodejů, pokud se neprodá asi 24 milionů kusů. . Samozřejmě s ohledem na to, že skutečné ASP není tak drahé (nedostane se na úroveň 200 USD), je nutné sériově vyrábět čipy s číslem blízkým tomu, ne-li 50 milionům, a objem výroby Intel 7 je řádově krátká. 10nm SuperFin používaný v TigerLake a IceLake-SP však nemá dostatečnou pracovní frekvenci a návrat k 14nm se nyní neplánuje. V důsledku toho si myslím, že výroba třídy Alder Lake Low End (Celeron až Core i3) byla zadána společnosti TSMC.

Původně má Intel 7 specifikace, které jsou téměř podobné TSMC N7P, a přechodem na N5 lze velikost oblasti zmenšit o 45 %, spotřebu energie lze snížit o 20 % nebo zvýšit provozní frekvenci o 15 %. %. být hotovo. Původně má Alder Lake for Desktop konfiguraci 6C + 0E kromě konfigurace 8P + 8E (Photo02) je zveřejněna zde a zdá se, že tento produkt 6C + 0E + 32EU je svěřen TSMC. Stručně řečeno, Core i3 nebo méně. Pokud jsou odstraněna dvě P-jádra a všechna E-jádra, velikost matrice se vejde asi 160 mm2, i když je použit Intel 7. Po vyříznutí bude mít velikost přibližně 90 mm2. Potom se počítá, že z jednoho 300mm waferu lze získat více než 700 kusů a očekává se, že náklady na čip budou dostatečně sníženy na to, aby se daly zaplatit, i když bude probíhat externě. Navíc, protože počet kusů, které lze získat, je velký, například měsíční produkce 10 000 kusů může zajistit 7 milionů kusů a 21 milionů kusů za 3 měsíce. Zdá se, že objednávky na produkty 14nm generace budou brzy zrušeny, ale zrušení objednávek neznamená, že dodávky budou okamžitě pozastaveny a dodávky produktů 14nm generace budou ještě chvíli pokračovat. Udržet zásilky v blízkosti nebude těžké na 50 milionů jednotek (problém je, zda N5 od TSMC dokáže zajistit 10 000 jednotek měsíčně?). Toto spuštění by mohlo začít již v prvním čtvrtletí.

Nyní je další Raptor Lake. Ve skutečnosti je kódové označení pro Raptor Lake odhaleno od loňského roku. První jasně ukázaná je stránka Product List SATA-IO (Photo03). Na konci jsou dva PCH, ale oba jsou „Kódové označení Alder-Raptor Lake PCH-S SATA Controller“, což naznačuje, že PCH je stejný pro Alder Lake a Raptor Lake. Poté se sem tam objevily informace a existence Raptor Lake je již zcela jistá.

Očekává se, že Raptor Lake, jak jsem již zmínil, se bude vyrábět v N3 společnosti TSMC. existují dva důvody

Je to kolem. Může však Alder Lake zcela nahradit Rapter Lake? Myslím, že i toto je obtížné. Důvodem je kapacita TSMC N3. Článek pana Tsuyoshi Hattoriho o Process jsem představil dříve, ale před pronásledováním AMD postrádal Intel výrobní kapacitu pro pokročilé procesy do té míry, že chtěl veškerou kapacitu Fab18B, kdyby ji potřeboval. To se splní po roce 2024, kdy zahájí provoz Fab od Intelu, který je aktuálně ve výstavbě v Arizoně. Na TSMC se budeme muset spolehnout minimálně v letech 2022–2023.

Osobně jsem však měl o N3 pochybnosti. Je to proto, jak bylo vysvětleno dříve v procesu TSMC, očekává se, že sériová výroba samotného N3 bude zahájena ve druhém čtvrtletí roku 2022, ale očekává se, že sériová výroba jiná než Apple se přesune do roku 2023. Spíše se zdálo pravděpodobnější N4 nebo N4P. S takovými hlášeními se to ale může nečekaně podařit zajistit.

Zdá se tedy, že tento proces jde s N3, ale informace, které jsem zatím slyšel o jiných konfiguracích, jsou

nebo něco takového. Samotné jádro se zdá být v zásadě stejné jako Golden Cove + Gracemont od Alder Lake, i když je potřeba udělat ještě nějakou práci. Mohlo by to být nějaké zlepšení? Pro designérský tým bude spíše hodně práce, aby jádro navržené pro Intel bylo kompatibilní s TSMC N3.

Ačkoli to nejsou potvrzené informace jinde, spotřeba energie může být poněkud snížena tím, že se jedná o proces TSMC. Kromě toho se také mluví o montáži DLVR (Digital Linear Voltage Regulator) na straně balení. Toto je příběh popsaný v patentu získaném společností Intel v červenci 2021 a jeho záměrem je zlepšit účinnost napájení instalací FIVR (Fully Integrated Voltage Regulator) nebo DLVR do balíčku CPU. , V příkladu popsaném v patentu, když jádrem protéká proud 40A, je možné zlepšit účinnost spotřeby energie až o 25 % (Foto04). Bude to nainstalováno v Raptor Lake? To je to, o čem mluvím.

Tento patent však znamená, že když je zátěž střední, existuje nesoulad mezi napětím, které jádro původně potřebuje řídit, a napětím, které je skutečně dodáváno, a to je opraveno regulátorem napětí na čipu Je to příběh, jak zabránit zbytečnému zvýšení napětí zakrytím. Důvod, proč dochází k nesouladu, je ten, že PMIC (Power Management IC) je mimo balíček a vydání požadavku od jádra CPU a změna napětí podle zátěže nějakou dobu trvá. Strana CPU proto vždy požaduje o něco vyšší napětí, než je požadované napětí, a i když je nutné náhle zvýšit napětí, požadavek je vydán PMIC a získává se marže, dokud se neprojeví. , Umístěním sekundy regulátoru napětí na obalu, je možné rychle dodat napětí blízké požadovanému napětí, čímž odpadá nutnost marně žádat vyšší napětí. Výsledkem je snížení ztrát a spotřeba energie může být snížena až o 25 %. To je ale účinné v případě střední zátěže, kde dochází ke kolísání napětí, ale při plném rozběhu nedochází ke změně napětí ani k zaváhání a napětí je vždy na maximálním nastavení, takže např. Foto04 V případě 70A, je vidět, že míra zlepšení je 0. V tomto smyslu je to užitečné pro mobilní zařízení a může to ocenit T SKU na Desktopu, ale nepřispívá to ke snížení TDP (nebo spíše PL1 nebo PL2) K SKU, které jsou plně napájené.

Původně Intel integroval FIVR do balíčku CPU v generaci Haswell a odstranil jej v generaci Skylake. Je to proto, že FIVR na čipu dokáže efektivně zvládnout vysoký výkon, ale je méně účinný při nízkém výkonu (hlavně kvůli omezením indukčního balíčku). AMD to bere v úvahu a implementuje regulátor LDO.

Vrátíme-li se k příběhu, je trochu záhadou, zda je tento DLVR skutečně nainstalován v Raptor Lake. Nepřekvapilo by mě, kdyby to implementovali, ale udělají to s Raptor Lake, který používá proces TSMC? Je to docela záhada a mám pocit, že to udělám u dalšího Meteor Lake.

Poslední je Meteor Lake, ale zatím neexistuje žádný konkrétní příběh. Nicméně například, ačkoli se dekodér jmenoval Peak 6 instrukcí / cyklus, Sustained měl 5 instrukcí / cyklus, ale očekávám vylepšení, jako je počet instrukcí Decode v Sustained, že se o něco více zvýší a latence Cache se sníží. vypadá to, že by to bylo v pohodě. V této generaci se také bude jednat o kompletní konfiguraci modulu a CPU Die, I/O Die a GPU Die budou součástí Foveros.

Na snímku v době oznámení tohoto balíčku, Intel 4, byl nakreslen jako tři matrice, CPU, PCH a GPU, ale ve skutečnosti je to dlaždice CPU, dlaždice SoC a dlaždice GT, jak je znázorněno na Obrázek 1 Kromě toho se zdá, že existuje dlaždice IOE, která obsahuje řadiče PCIe a Thunderbolt.

Přestože obrázek 1 je pro mobilní zařízení, dlaždice IOE mohou být vynechány pro stolní počítače. Jako pisatel jsem si myslel, že CPU Tile bude oddělený, například P-Core Tile a E-Core Tile, ale zdá se, že v takovém rozsahu rozdělen nebude.

Pokud jde o SoC Tile, hovoří se také o tom, že GNA bude v této generaci Meteor Lake zrušena a místo toho bude zahrnuto AI jádro Movidius získané Intelem. Přestože se Intel GNA chlubí vysokým poměrem výkon/spotřeba, absolutní výkon procesoru je spíše nízký, takže často slýcháme, že výkon je nedostatečný, i když se jej pokusíte použít přes OpenVINO od Intelu. Existuje také příběh, že aplikace, které používají OpenVINO, nejsou vhodné pro GNA. Možná jsem se rozhodl přejít.

Teď je toto samotné Meteor Lake zabaleno s Foveros. Když se podíváte na video ve vydání „Intel Breakthroughs Propel Moore's Law Beyond 2025“, které Intel oznámil 11. prosince 2021, příkladem použití Foveros (Photo05) je Meteor Lake a je jich mnohem více. Říká se, že je to možné kombinovat dlaždice různých velikostí (Photo06) a dlaždice různých velikostí (Photo07). Meteor Lake je konzervativní konfigurace, která vyžaduje bezpečnostní opatření, protože jde o první generaci procesorů s konfigurací Tile pro spotřebitele a další dělení Tile může být po Meteor Lake.

Jak je uvedeno v Process, tento Meteor Lake je Intel 4. V případě takového Multi-Tile se však "Který vyrábí Intel 4?" Například dlaždice CPU a dlaždice GPU mohou být Intel 4 a dlaždice SoC a dlaždice IOE mohou být Intel 7. Na to, abychom se o tom dozvěděli více, si budeme muset ještě chvíli počkat.